**2D Electronics**

# Electronic Devices and Circuits Based on Wafer-Scale Polycrystalline Monolayer MoS<sub>2</sub> by Chemical Vapor Deposition

Lin Wang, Li Chen, Swee Liang Wong, Xin Huang, Wugang Liao, Chunxiang Zhu, Yee-Fun Lim, Dabing Li, Xinke Liu,\* Dongzhi Chi,\* and Kah-Wee Ang\*

2D layered materials such as graphene and transition-metal dichalcogenides (TMDCs) have emerged as promising candidates for next-generation nanoelectronic applications due to their atomically thin thicknesses and unique electronic properties. Among TMDCs, molybdenum disulfide (MoS<sub>2</sub>) has been extensively investigated as a channel material for field-effect transistor (FET) and circuit realization. However, to date most reported works have been limited to exfoliated MoS<sub>2</sub> nanosheets primarily due to the difficulty in synthesizing large-area and high-quality MoS<sub>2</sub> thin film. A demonstration of wafer-scale monolayer MoS<sub>2</sub> synthesis is reported by chemical vapor deposition (CVD), enabling transistors, memristive memories, and integrated circuits to be realized simultaneously. Specifically, building on top-gated FETs with a high- $\kappa$  gate dielectric (HfO<sub>2</sub>), Boolean logic circuits including inverters and NAND gates are successfully demonstrated using direct-coupled FET logic technology, with typical inverters exhibiting a high voltage gain of 16, a large total noise margin of 0.72  $V_{DD}$  at  $V_{DD}$  = 3 V, and perfect logic-level matching. Additionally, resistive switching is demonstrated in a MoS<sub>2</sub>-based memristor, indicating that they have great potential for the development of resistive random-access memory. By virtue of scalable CVD growth capability, the way toward practical and large-scale electronic applications of MoS<sub>2</sub> is indicated.

geometry.<sup>[1-3]</sup> The discovery of graphene has attracted intense attention due to its superior conductivity property. However, graphene is not a good choice for logic application because of its gapless nature, impeding the fabrication of devices with high on/off ratio or amplifiers requiring a voltage gain of >1.<sup>[4,5]</sup> To overcome the bandgap limitation, transition metal dichalcogenides, a different class of 2D materials, have been discovered and gained extensive research interest.<sup>[6,7]</sup> They usually consist of a layer of transition metal atoms (such as Mo, W, and Ti) sandwiched between two layers of chalcogen atoms (such as S, Se, and Te). Among them, molybdenum disulfide (MoS<sub>2</sub>), due to its direct moderate bandgap (1.8 eV for monolayer) and high electron mobility, has become the most investigated 2DLM for realizing future-generation electronic and optoelectronic devices.<sup>[8]</sup> To date, functional devices such as field-effect transistors (FETs),<sup>[9-13]</sup> logic circuits,<sup>[14-18]</sup> and optoelectronic devices<sup>[19]</sup> based on MoS<sub>2</sub> have been widely demonstrated. For example, monolayer MoS2-based transis-

# 1. Introduction

Recently, 2D layered materials (2DLMs) have emerged as promising candidates for next generation nanoelectronic applications owing to their unique electronic properties and ultrathin

Dr. L. Wang, L. Chen, Dr. X. Huang, Dr. W. Liao, Prof. C. Zhu, Prof. K.-W. Ang Department of Electrical and Computer Engineering National University of Singapore 4 Engineering Drive 3, 117583, Singapore E-mail: eleakw@nus.edu.sg Dr. L. Wang, L. Chen, Dr. X. Huang, Dr. W. Liao, Prof. C. Zhu, Prof. K.-W. Ang Centre for Advanced 2D Materials National University of Singapore 6 Science Drive 2, 117543, Singapore

D The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/aelm.201900393.

#### DOI: 10.1002/aelm.201900393

tors have been implemented with on/off ratios achieving  $10^8$ and electron mobility up to  $320 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1,[9,15]}$  However, most of the reported MoS<sub>2</sub> devices rely on mechanically exfoliated MoS<sub>2</sub> nanoflakes and a vast majority of them remain at the level of discrete transistors. Although exfoliated flakes are

Dr. S. L. Wong, Dr. Y.-F. Lim, Dr. D. Chi

E-mail: dz-chi@imre.a-star.edu.sg

Changchun Institute of Optics

Fine Mechanics and Physics

Chinese Academy of Sciences

E-mail: liuxinke@ciomp.ac.cn

Changchun 130033, P. R. China

Prof. D. Li, Prof. X. Liu

Institute of Materials Research and Engineering

A\*STAR 2 Fusionopolis Way, 138634, Singapore

State Key Laboratory of Luminescence and Applications

of high quality, the micromechanical cleavage approach lacks the systematic control of the 2D material in terms of thickness, size, and uniformity, thus hindering their actual integration into scalable device fabrication. To address such issue, considerable efforts have been dedicated to exploring large-scale growth of atomically thin MoS<sub>2</sub> films with controlled chemical composition and physical dimension. Until now, various approaches have been demonstrated including liquid exfoliation, atomic layer deposition (ALD), chemical vapor deposition (CVD), and metalorganic chemical vapor deposition (MOCVD).<sup>[20,21]</sup> For liquid exfoliation, although it could guarantee the production of a relatively large quantity of materials, it lacks a good control of the flake size and thickness, and the resulting materials tend to be contaminated with excessive impurity doping.<sup>[22]</sup> Regarding ALD process, it usually results in low crystallinity of the produced film.<sup>[23,24]</sup> Besides, highly uniform MoS<sub>2</sub> monolayer film was produced by a well-designed MOCVD process, but the use of vapor phase reactants makes the growth process more sophisticate.<sup>[25]</sup> In comparison, CVD process based on solidphase precursors allows the growth of relatively high quality crystals with a well-controlled lateral size and layer thickness in a cost-effective way.<sup>[21,26]</sup> To date, significant progress has been made in growing large-area MoS<sub>2</sub> film of improved quality, by tuning of process parameters (operating pressure, temperature, concentrations of the chemical precursors, etc.), reactor geometry, and choice of chemical precursors, and by introducing seed promotors and gases such as oxygen.<sup>[27-30]</sup> However, few works have been done in regulating the flux and concentration gradient of the chemical precursors using reactive barriers. Meanwhile, despite the decent performance of individual MoS<sub>2</sub> transistor, higher level electronic circuits based on largescale MoS<sub>2</sub> are required toward ultimate practical applications. Over the past years, the progress in CVD-growth of large-area atomically thin MoS<sub>2</sub> film renders it possible for the correlated realization of high-yield integrated circuits. Inspiringly, a microprocessor has recently been demonstrated on the basis of large-scale bilayer MoS<sub>2</sub> grown by CVD.<sup>[31]</sup> Nevertheless, the fabrication still required a complicated process of transferring the thin film onto a target substrate, similar to many reported MoS<sub>2</sub> works.<sup>[17,32,33]</sup>

Here, we report a scalable approach to fabricating fundamental building blocks of digital electronic circuits using large scale monolayer MoS<sub>2</sub> synthesized via CVD. Particularly, for growing MoS<sub>2</sub> film, an additional Ni foam is added as a barrier to limit the deposition rate of chemical precursors, which enables an even distribution of reactants on the substrate for achieving continuous MoS<sub>2</sub> film with improved quality. Then we fabricated transistors on the as-grown MoS<sub>2</sub> in a straightforward manner without a transfer process, thus ensuring the entire fabrication process fully compatible with existing Si technology. The resultant transistors exhibit promising performance with a high on/off ratio up to 10<sup>6</sup> and a subthreshold swing of  $\approx 130$  mV dec<sup>-1</sup>, indicating a good control over short channel effect. Apart from discrete transistors, Boolean logic functions including NOT (or inverter) and NAND gates are demonstrated using direct-coupled FET logic (DCFL) technology through a careful circuit design. The inverter exhibits a voltage-match characteristic and a high voltage gain of  $\approx 16$  at  $V_{DD} = 3$  V. Particularly, the noise

margin of 0.41  $V_{\rm DD}$  for low input voltage (NM<sub>L</sub>) and 0.31  $V_{\rm DD}$  for high input voltage (NM<sub>H</sub>) manifest its suitability for realizing complex cascaded circuits. Additionally, we show the existence of resistive switching behavior in MoS<sub>2</sub> transistorbased structure, implying its high potential for resistive random access memory-relevant application such as neuromorphic computing.

## 2. Results and Discussion

## 2.1. Monolayer MoS<sub>2</sub> Thin Film Synthesis

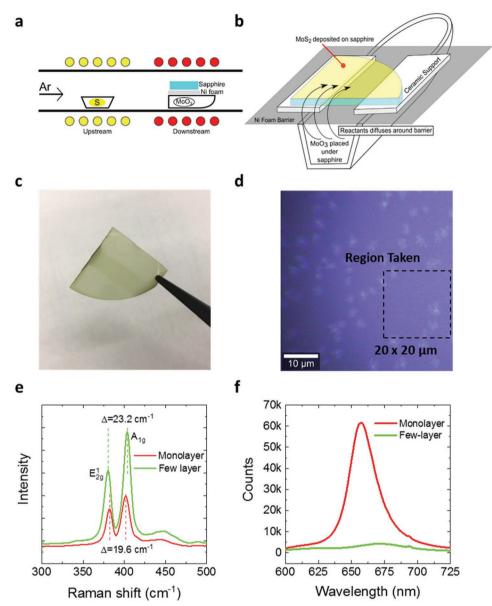

The monolayer MoS<sub>2</sub> was synthesized on a commercially available c-plane (0001) sapphire substrate in a quartz tube furnace. Compared with SiO<sub>2</sub>, the use of sapphire as substrate is expected to result in MoS2 film growth of higher quality, owing to its single crystal structure and the commensurability of the sapphire lattice with MoS2.<sup>[34,35]</sup> MoO3 and sulfur were used as the precursors. Figure 1a,b schematically illustrates the arrangement of our tube furnace for the MoS<sub>2</sub> growth. Different from previous works of CVD-grown MoS2, a Ni foam was employed to serve as the reactive barriers for limiting the deposition rate of the chemical precursors. Ni is known to react with MoO<sub>3</sub>, thus it functions not only as a physical barrier but also as a chemically reactive trap of MoO<sub>3</sub>, which allows greater regulation of the precursor flux during the growth process compared with an inert physical barrier, hence the growth of MoS<sub>2</sub> film with improved quality. Additionally, we noticed that the absence of a Ni foam would result in a reduced coverage of 2D MoS<sub>2</sub> on the substrate.

An optical image of the CVD-grown MoS<sub>2</sub> film on a 1/4 2-inch transparent sapphire substrate is shown in Figure 1c. Following the growth, Raman and photoluminescence (PL) measurements were performed on selected regions (Figure 1d) at room temperature with a 532 nm laser for excitation. As shown in Figure 1e, two Raman peaks are observed at 386.5 and 406.1  $\rm cm^{-1}$ , corresponding to the  $E_{2g}$  and  $A_{1g}$ vibration modes of MoS<sub>2</sub>, respectively. Furthermore, the separation of 19.6  $\rm cm^{-1}$  between the  $E_{2g}$  and  $A_{1g}$  mode peaks confirms the monolayer nature of the grown film, whereas the larger separation of 23.2 cm<sup>-1</sup> of the two modes indicates the formation of few-layer MoS2 (the gray dots as shown in Figure 1d) during the growth process. The ratio of the monolayer area to the entire MoS2 film was estimated to be 82.7%, evidencing the dominance of monolayer MoS<sub>2</sub> growth (Section S1, Supporting Information). One future direction to reduce few-layer MoS2 growth is to identify the process window in which a complete MoS<sub>2</sub> monolayer emerges prior to the development of few-layer islands, through further tuning the synthesis parameters. In Figure 1f, the PL peak at the wavelength of ≈657 nm is observed, which is consistent with the  $\approx 1.8$  eV bandgap for monolayer MoS<sub>2</sub>. Besides, the PL intensity for monolayer MoS<sub>2</sub> is more than one order higher than for the few-layer MoS<sub>2</sub>, as a result of their respectively direct and indirect bandgaps. Furthermore, the relatively high uniformity of the single layer film has been revealed by PL mapping over a 20  $\mu$ m  $\times$  20  $\mu$ m region (Section S1, Supporting Information).

www.advancedsciencenews.com

ANCED

**Figure 1.** Growth and material characterization of the large-scale CVD-grown monolayer  $MoS_2$  film. a) Crucible placements in tube furnace for  $MoS_2$  growth with sulfur (S) and  $MoO_3$  in the upstream and downstream regions, respectively. b) An illustration of detailed arrangement of the substrate, precursor flow, and Ni foam for  $MoO_3$ -containing crucible. c) Optical image of the monolayer  $MoS_2$  thin film on a quarter 2-inch sapphire substrate. d) Optical image of the chosen region for the measurement. e) Raman spectrum of the monolayer  $MoS_2$  within the grown film. The 19.6 and 23.2 cm<sup>-1</sup> distance between the  $A_{1g}$  and  $E_{2g}^1$  peaks correspond to monolayer  $MoS_2$  and few-layer  $MoS_2$ , respectively. f) Photoluminescence (PL) spectrum of the  $MoS_2$  film. The PL intensity for monolayer  $MoS_2$  is much higher than for the few-layer  $MoS_2$ , as a result of their respective direct and indirect bandgaps.

#### 2.2. Device Fabrication

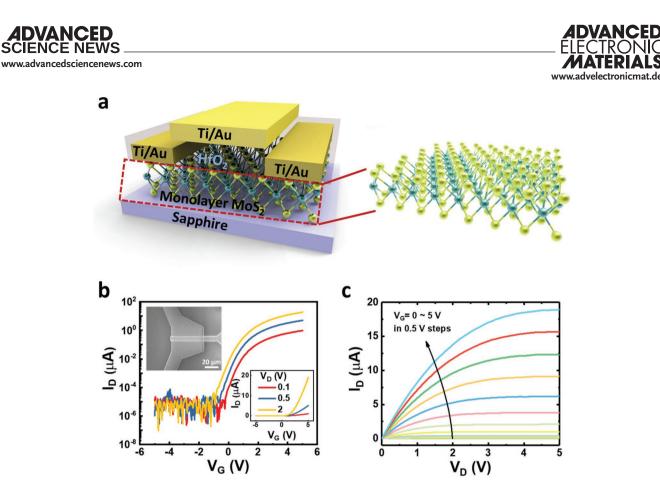

Electronic devices and circuits were directly fabricated from the as-grown monolayer  $MoS_2$ . Active regions for transistors were defined in a patterning step followed by a CHF<sub>3</sub>-based reactive ion etching process. After that, 5 nm/70 nm Ti/Au source/drain electrodes were formed by electron beam evaporation following another patterning step. Because of the insulating substrate, we employed top-gate architecture for the device fabrication, which is considered being more compatible with the existing

technology. A 20 nm thick  $HfO_2$  with a permittivity of 15 was grown by ALD at 150 °C to serve as gate dielectric (Section S2, Supporting Information). Finally, another 5 nm/70 nm Ti/Au was deposited followed by a standard lift-off process to form the top-gate electrode. Particularly, for logic circuits, a via-hole connecting the source and gate terminals of the pull-up transistor was defined prior to the gate metal deposition. A schematic of the MoS<sub>2</sub>-based top-gated transistors is given in **Figure 2a** and more details on the fabrication process can be found in the Experimental Section.

**Figure 2.** Characterization of a representative MoS<sub>2</sub> transistor. a) Schematic of the top-gated MoS<sub>2</sub> transistor. b) Transfer characteristics of the device, showing an evident n-type behavior with a high on/off ratio up to  $10^6$  and a low subthreshold swing (SS) of 130 mV dec<sup>-1</sup>. Inset is a scanning electron microscope (SEM) image of the device. c) Output characteristics ( $I_D$ – $V_D$ ) of the device. The current saturates at  $V_D$  = 5 V.

#### 2.3. Characterization of MoS<sub>2</sub> Field-Effect Transistors

We first investigated the electrical properties of the MoS<sub>2</sub> transistors. A  $6 \times 6$  array of MoS<sub>2</sub> transistors were fabricated over a 2 mm × 3 mm area (Section S3, Supporting Information), with a channel length (L) of 3  $\mu$ m and a channel width (W) of 45 µm. The transfer characteristics of a representative MoS<sub>2</sub> transistor at different drain biases are plotted in Figure 2b. Apparently, the MoS<sub>2</sub> FET exhibits a typical n-type conduction behavior with a current on/off ratio exceeding 10<sup>6</sup> that is sufficient for logic circuits application.<sup>[14]</sup> By using the equation  $SS = (d \log_{10}I_D/dV_G)^{-1}$ , where  $V_G$  is the gate bias and I<sub>D</sub> is the drain-source current, a small subthreshold swing of  $\approx 130 \text{ mV dec}^{-1}$  is determined. This value indicates a steep switching characteristic of the device and is likely to be further reduced by downscaling the dielectric thickness. Furthermore, the field-effect electron mobility is extracted by using the equation  $\mu_{\rm FE} = g_{\rm m} \times (L/WC_{\rm OX}V_{\rm D})$ , where  $g_{\rm m}$  is the transconductance of the transistor,  $C_{\text{OX}}$  is the capacitance of gate dielectric per unit area, and  $V_{\rm D}$  is the drain to source voltage bias. For the fabricated transistors, typical electron mobility is in the range from 0.1 to 1 cm²  $V^{-1}\ s^{-1},$  with the highest value reaching 3 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (Section S4, Supporting Information). These values are slightly lower than those in representative works on CVD-MoS<sub>2</sub><sup>[26,36]</sup> and can be ascribed to smaller monocrystalline domain sizes as well as sparse growth of few-layer MoS<sub>2</sub> islands that cause more significant carrier scattering. The low carrier mobility for CVD grown MoS<sub>2</sub> in comparison with exfoliated MoS<sub>2</sub> nanoflakes can be attributed to intrinsic defects, grain boundaries, as well as interface scattering due to the atomically thin nature of the film, which highlights the demand of further advancement in the material synthesis toward practical application. One way to enhance the charge mobility is to increase monocrystalline domain sizes for reduction of grain boundary scattering. This can be potentially realized by having a separate control of MoO<sub>3</sub> precursor powders and substrate temperature using a three-zone growth reactor. Consequently, individual heating temperatures can be applied to the substrate and MoO3 source, where a lower temperature for MoO<sub>3</sub> is used to reduce MoO<sub>3</sub> sublimation and therefore MoS<sub>2</sub> nucleation density while adatom surface mobility is still high on the growth substrate at a higher temperature.<sup>[37]</sup> However, this strategy is beyond the capability of our setup at present stage. Alternatively, a transfer of the grown film to another substrate has proved helpful in improving device performance,<sup>[38]</sup> except that this would require a reliable and high throughput large scale transfer from grown substrate to target substrate.<sup>[39]</sup>

The output characteristics of the transistor at various top gate voltages from 0 to 5 V in a 0.5 V step are given in Figure 2c. The  $I_D$ -V<sub>D</sub> curves show linear behavior at low drain bias voltages, indicating that a near-Ohmic contact is achieved as a result of the low potential barrier between Ti and MoS<sub>2</sub>. More importantly, clear current saturation behavior is observed at high source–drain bias as featured by the close-to-zero drain–source conductance (as defined by  $G_{DS} = dV_{DS}/dI_{DS}$ ), which is desired for logic circuit operation in this regime. In addition,

the well-matched onset of saturation and the gate overdrive suggest its potential for constructing circuits with logic-level matching characteristic.

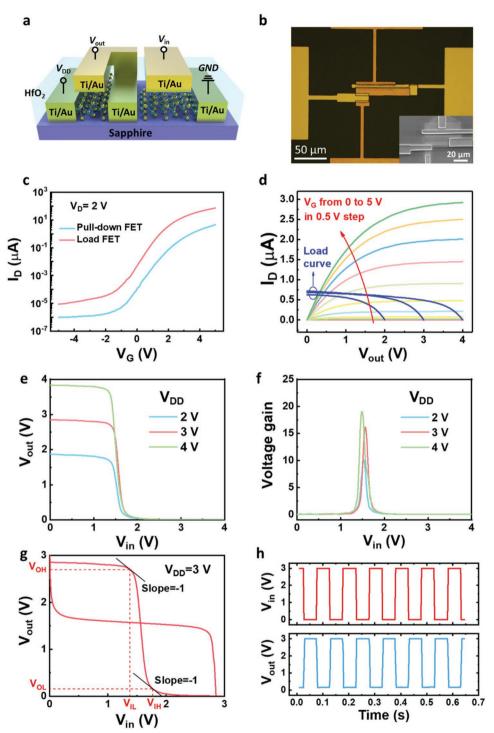

## 2.4. Characterization of MoS<sub>2</sub> Based Boolean Logic Circuits

By leveraging on the discrete transistors, we then constructed integrated logic circuits based on the CVD-grown monolayer MoS<sub>2</sub>. To this end, we have fabricated Boolean logic gates such as NOT and NAND gates, which form the fundamental building blocks for the realization of advanced digital circuits. The circuit was implemented by N-type metal-oxide-semiconductor logic in a similar way to the work in ref. [31], where both pull-up (load) and pull-down transistors were n-type enhancement-mode FETs. The gate and source electrodes of the pull-up transistor are connected together to serve as the output terminal. Such strategy allows us to design the width/length (W/L) ratios of the two FETs to achieve suitable switching threshold voltage as well as noise margin of the inverter, which are crucial to ensure the ability of constructing cascaded circuits. For example, two transistors with the same W/L ratio would cause a left shift of  $V_{\rm m}$  and degrade the noise immunity. In our case, the W/Lratios were designed to be 50  $\mu$ m/1.5  $\mu$ m and 7  $\mu$ m/3.5  $\mu$ m for the pull-up transistor and the pull-down transistor, respectively, to shift V<sub>m</sub> toward a more positive value for logic-level matching. The transfer characteristics of the two E-mode transistors are shown in Figure 3c. The more than ten times higher current for the pull-up FET in comparison to the pull-down FET manifests the successful control of device characteristics by geometrical scaling. The characteristics of the inverter are in principle determined by the output curves of the pull-down FET and the load curve of the pull-up FET (Figure 3d). Typically, the pull-down transistor operates in the triode regime or saturation regime, whereas the pull-up transistor operates in the subthreshold regime and acts as a current source over a large drain voltage range. The performance of a logic inverter is usually examined by its voltage transfer characteristics. As plotted in Figure 3e, the output signal of the inverter shows a clear opposite logic-level to its input voltage for a wide range of supply voltage  $V_{DD}$  from 2 to 4 V. The DC voltage gains, as defined by  $V_{\text{gain}} = -dV_{\text{OUT}}/dV_{\text{IN}}$  which indicates the sensitivity of  $V_{out}$  switching to  $V_{in}$ , are extracted and plotted in Figure 3f. The highest gains are found to be 10, 16, and 19 for  $V_{DD} = 2$ , 3, and 4 V, respectively, which, being much larger than 1, indicates the ability of our n-logic inverter to serve as the building block of multistage circuits. Additionally, the noise margin plays a crucial role in determining the tolerance of an inverter to input signal noise and consequently the reliability of cascaded logic circuits. For our DCFL inverter, the noise margin for low input voltage and high input voltage are extracted to be  $NM_L = 0.41 V_{DD}$  and  $NM_H = 0.31 V_{DD}$  for  $V_{DD} = 3$  V, respectively (Figure 3g). The noise margin of >30% for both NM<sub>L</sub> and NM<sub>H</sub> implies the potential of the inverter to be integrated into a complex circuit system. Besides, we performed the AC measurement on the inverter. Figure 3h shows the temporal evolution of  $V_{in}$  and  $V_{out}$  for a  $V_{DD}$  = 3 V at a frequency of 10 Hz. It is clear that the output curve is opposite to the input curve. For a more quantitative analysis on the switching

performance of the inverter, the intrinsic delay time is determined by  $\tau = RC_{\rm p}$ , where R is the transistor resistance corresponding to the transistor drive current and  $C_p$  is the overall parasitic capacitance. The parasitic capacitance  $C_p$  is mainly contributed by the gate capacitance of the two FETs, and can be calculated by  $C_{\rm p} = (L_1 W_1 + L_2 W_2) \varepsilon_{\rm r} \varepsilon_0 / t_{\rm ox}$ , where  $\varepsilon_{\rm r}$  is the dielectric constant of HfO<sub>2</sub>,  $t_{\rm ox}$  is gate dielectric thickness, and  $\varepsilon_0$  is the permittivity of free space. As a result,  $C_p = 0.66$  pF is obtained. In addition, the peak drive current of the inverter at  $V_{dd} = 3$  V is measured to be  $\approx$ 35 nA. Therefore, the intrinsic delay can be estimated to be  $\tau_{\text{intrinsic}} = C_{\text{p}}V_{\text{DD}}/I = 57 \ \mu\text{s}$ , indicating that the inverter can potentially operate at a maximum frequency of  $f = 1/2\pi\tau = 2.8$  kHz. Here it is to note that other factors such as imperfect Ohmic character at source/drain contacts and overlapping gate area larger than  $L \times W$  of the device channels are likely to further degrade the switching frequency due to additional capacitive effect. We emphasize that similar to other works of integrated circuits based on large-scale MoS<sub>2</sub>, the relatively low operation speed in this work is primarily a consequence of the low carrier mobility and the large parasitic capacitance resulted from large gating area. Consequently, improvement in frequency performance can be anticipated by shortening the device channel length to reduce simultaneously the gate capacitance and the channel resistance. Substantially, improving the film quality to enable a higher carrier mobility is necessary for the enhancement of the performance of MoS<sub>2</sub> circuits toward their realistic application in digital electronics. Furthermore, we compared our device with other reported MoS<sub>2</sub>-based inverters (Section S5, Supporting Information). It is noticed that our logic circuit can deliver a decent voltage gain and matched logic voltage. Furthermore, while most of the reported MoS<sub>2</sub> based inverters relied on exfoliated MoS<sub>2</sub> flakes or required a complicated transfer process, thus being incompatible with existing Si technology, our work demonstrates a more practical and scalable approach to realizing large scale MoS<sub>2</sub> integrated circuits through a straightforward fabrication process on the as-used substrate.

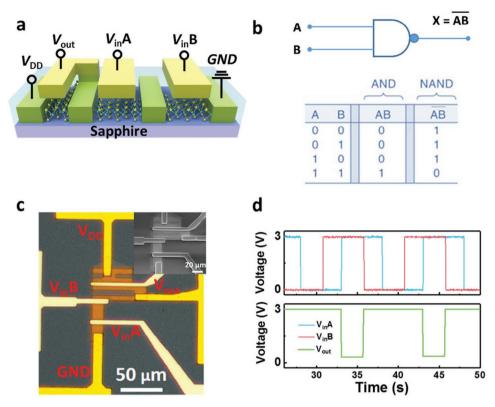

Next, we further demonstrate a two-input Boolean NAND gate, which represents one of the two basic logic gates (together with NOR gate) with universal functionality. Figure 4a shows the schematic of the fabricated NAND circuit. The two-input NAND gate was implemented by connecting two pull-down transistors in series with the identical dimension of W/L (2  $\times$  7.5  $\mu$ m/3.5  $\mu$ m) to maintain logiclevel matching. The Boolean expression and NAND gate function are described in Figure 4b and the optical image of the NAND is given in Figure 4c. Figure 4d shows the timing diagram of the NAND gate. Apparently, it outputs a low logic state only when both input voltages are at high logic level. In contrast, with either or both inputs being equal to 0 V (logic state 0), the output voltage is approaching 3 V supply voltage  $V_{DD}$  (i.e., logic state 1) because at least one of the two pull-down transistors is forbidding current flow. Thus, the result demonstrates clearly the functionality of an NAND gate. Since more complicated logic circuits including other types of logic gates can be implemented using a combination of NAND gates, it is therefore plausible to manufacture fully integrated logic circuits based on large-scale CVD-grown monolayer MoS<sub>2</sub>.

**Figure 3.** Characterization of the  $MoS_2$ -based logic inverter. a) Schematic and b) an optical image of the n-logic  $MoS_2$ -based inverter. Inset in (b) is an SEM image of the circuit. c) Transfer characteristics of the two FETs for inverter design. d) Output characteristics of the pull-down FET plotted together with load curves of the inverter for  $V_{DD} = 2$ , 3, and 4 V, respectively. e) Transfer characteristics of the inverter. The voltage is well matched with a supply bias ranging from 2 to 4 V. f) Voltage gain as a function of input voltage of the inverter. A high gain of 19 is achieved at  $V_{DD} = 4$  V. g) Noise margin properties of the inverter. The extracted noise margins are 0.41  $V_{DD}$  and 0.31  $V_{DD}$  for NM<sub>L</sub> (=  $V_{IL} - V_{OL}$ ) and NM<sub>H</sub> (=  $V_{OH} - V_{IH}$ ), respectively, indicating a good tolerance to noise. h) Dynamic response of the inverter at a frequency of 10 Hz, showing unambiguously the inversion functionality.

#### 2.5. Characterization of MoS<sub>2</sub> Based Memristive Memory

Over the past decade, memristors have been demonstrated and considered as an important candidate for future electronics for

novel computing technologies such as in-memory computing and neuromorphic computing.<sup>[40,41]</sup> In recent years, 2DLMs have started to attract intense research interest for their potential in memristive device application. For instance, they can

**Figure 4.** Characterization of the  $MoS_2$ -based NAND gate realized in this work. a) Schematic of the NAND gate. b) Boolean expression and logic function of the NAND gate. The NAND gate outputs a logic low voltage only when both the input voltages are at a logic high voltage. c) Optical image of the NAND gate. Inset is an SEM image of the circuit. d) Timing diagram of the NAND gate. The device outputs a high level of 3 V when either or both of the inputs are at 0 V.

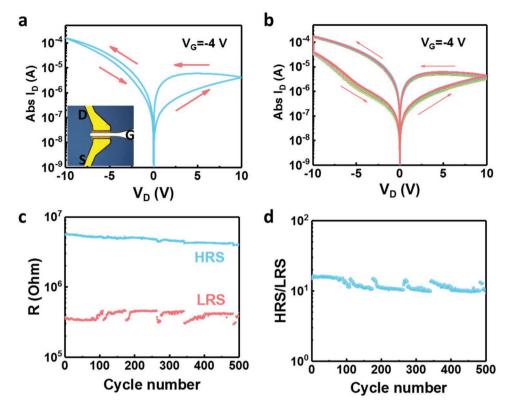

be used as the core switching medium in metal-insulatormetal-structured two-terminal devices.<sup>[42-44]</sup> Particularly, among various 2D materials, polycrystalline MoS<sub>2</sub> synthesized by CVD has shown the prospect in fabricating memristive components.<sup>[45–47]</sup> Next, we show that the MoS<sub>2</sub> transistors can be exploited as memristive device with resistive switching characteristics. For this purpose, we investigated the electrical characteristics of a representative MoS<sub>2</sub> transistor. In Figure 5a, when the  $V_{\rm D}$  is swept from 0 to 10 V, the device is gradually switched from the high resistance state (HRS) to the low resistance state (LRS). The LRS is maintained for  $V_{\rm D}$  sweep from 10 V back to 0 V. Then a reset to the HRS is achieved through a  $V_{\rm D}$  sweep from 0 to -10 V, and the device retains its HRS during the sweep from -10 to 0 V. Such a state evolution in a closed-loop of  $V_{\rm D}$  sweep clearly manifests a bipolar analogue resistive switching behavior. The endurance characteristics of the device are examined by switching it between HRS and LRS in a consecutive 500 sweep cycles (Figure 5b). Based on this result, the resistance values corresponding to the HRS and LRS of the device are extracted at  $V_{\rm D} = 0.1$  V and plotted as a function of sweep cycles, as shown in Figure 5c. The switching ratio, defined as  $R_{\rm HRS}/R_{\rm LRS}$ , is calculated to be higher than 10, which is well comparable to previous work while using a much smaller voltage range.<sup>[45]</sup> We notice that by integrating an additional terminal, the memristors in our work is different from two-terminal memristive devices such as traditional TiO2-based ones and recently demonstrated MoS2-based atomristors.[42,48] Although the switching ratio might not be as high as in two-terminal memristors exhibiting abrupt resistance switching, the different structure is likely to provide new functionality that is inaccessible by two-terminal devices and will be exploited in our future work.<sup>[45]</sup> The resistive switching behavior can be attributed to the dynamic migration of the defects within the channel material. Indeed, various defects in MoS<sub>2</sub> have been observed experimentally in CVD-synthesized MoS<sub>2</sub> film, such as, single vacancy S ( $V_S$ ), double vacancy S ( $V_{2S}$ ), (5|7) Mo-Mo dislocation and (4|6) defect complex comprising a (5|7) S–S dislocation, and a double S vacancy  $V_{2S}$ .<sup>[49–51]</sup> In this work, the grown film was characterized by atomic force microscopy, and grain boundaries with 1-3 µm domain sizes have been revealed (Section S6, Supporting Information). Upon applying an external electric field, they will migrate favorably along grain boundaries toward or far from the electrode end of the device (depending on the bias polarity), resulting in dynamic tuning of the Schottky barrier heights and consequently resistance switching, as has been experimentally evidenced in polycrystalline MoS<sub>2</sub> devices on a Si/SiO<sub>2</sub> substrate.<sup>[45]</sup> In this regard, the switching behavior might vary from cycle to cycle due to the motions of defects taking place on the microscopic scale, which is common in different types of memristive devices.<sup>[43,52]</sup> Nevertheless, our device exhibits distinct resistance states over the 500 switching cycles, demonstrating its good endurance property. Further optimization of the performance will require a more-controllable defects engineering during as well as after the growth of the film.

**Figure 5.** Resistive switching behavior observed in top-gated transistor made from CVD-grown monolayer MoS<sub>2</sub>. a) Drain current ( $I_D$ ) of a MoS<sub>2</sub> transistor ( $W = 25 \ \mu\text{m}$ ,  $L = 1.5 \ \mu\text{m}$ ) as a function of the drain bias ( $V_D$ ) at a gate voltage of -4 V. The direction of  $V_D$  sweep is indicated by red arrows. Inset shows an optical image of the device. b)  $I_D - V_D$  curves for 500 consecutive sweeps at  $V_G = -4 \ V$  for the same device. The direction of  $V_D$  sweep is indicated by red arrows. c) Extracted resistance values corresponding to the high resistance state (HRS) and low resistance state (LRS) of the device as a function of sweep cycle number. The currents at  $V_D = 0.1 \ V$  in (b) are used for calculation. d) Switching ratio (defined by  $R_{\text{HRS}}/R_{\text{LRS}}$ ) as a function of the sweep cycle.

## 3. Conclusion

In conclusion, we have demonstrated a practical approach to realizing fundamental building blocks for digital electronics based on large-scale monolayer MoS<sub>2</sub> film synthesized via a CVD process. Top-gated MoS<sub>2</sub> transistors with a thin high- $\kappa$ gate dielectric were demonstrated, which exhibit an on/off ratio exceeding  $10^6$  and a subthreshold swing of  $\approx 130 \text{ mV dec}^{-1}$ , indicating a superior control of short channel effect over the widely explored back-gated transistor structure with thick SiO<sub>2</sub> gate oxide. By leveraging on DCFL technology, Boolean logic circuits including NOT (or inverters) and NAND gates were successfully realized, with the inverter achieving a high voltage gain of 16 and a large noise margin of 0.72  $V_{DD}$ . Additionally, the potential of MoS2-based transistors for memristive switching functionality was demonstrated, which holds promise for the development of neuromorphic computing architectures. This work paves the way toward realizing a fully integrated 2D electronics circuits with complex functionality and scalability based on CVD-grown monolayer MoS<sub>2</sub>.

## 4. Experimental Section

Chemical Vapor Deposition of  $MoS_2$ :  $MoS_2$  is deposited on a commercially bought c-plane (0001) sapphire (Al<sub>2</sub>O<sub>3</sub>) substrate

(Namiki Inc) in a quartz tube furnace (planarTECH LLC) with two separate upstream and downstream heating zones. In the downstream region, 4.5 mg of MoO<sub>3</sub> (99.98%, Sigma-Aldrich) is placed in a single open-end crucible with a piece of nickel foam (size 3.5 cm  $\times$  3 cm, 1 mm thickness with 400  $\mu m$  average pore size) placed directly above the MoO<sub>3</sub> powder. The sapphire is placed above the nickel foam, supported by two ceramic pieces. The arrangement of the MoO<sub>3</sub> crucible, nickel foam, and sapphire is similar to our previous work.<sup>[53]</sup> 950 mg of sulfur (99.998%, Sigma-Aldrich) is placed in the upstream zone, 40 cm away from the MoO<sub>3</sub> precursor.

The detailed process flow is as follow: The downstream region is first heated to 250 °C for 10 min for degassing purpose with the upstream zone kept at room temperature while an Ar flow of 200 sccm is maintained. The temperature is then ramped to 750 °C over 12 min and is maintained for an additional 13 min with an Ar flow of 50 sccm to allow MoS<sub>2</sub> deposition to occur. Afterward, the tube is allowed to naturally cool down to 650 °C prior to opening of the furnace heaters for rapid cooling through ambient exposure while the Ar flow is increased to 200 sccm. The pressure is maintained at 6 Torr during the entire process. This low pressure enviroment is considered the primary factor responsible for the growth of small domain sizes, in comparison with MoS<sub>2</sub> synthesis at a higher pressure.<sup>[53]</sup> It is to note that the relatively fast growth of MoS<sub>2</sub> film, in comparison with other works which might take much longer time,<sup>[39]</sup> is readily a result of the use of powder source as well as a much higher flux.

Device Fabrication: The device fabrication on sapphire substrate consisted of the following steps: First, metal markers for alignment purpose throughout the device fabrication process were fabricated by electron beam lithography (EBL: JOEL-6300FS) and subsequent metal deposition and lift-off process. Second, to define the active regions

for transistor fabrication, another patterning process was performed by Laser Writer (LW405B), and MoS<sub>2</sub> film was selectively etched by CHF<sub>3</sub>-based reactive-ion etching (RIE) technique. Third, 5/70 nm Ti/Au source/drain electrodes were formed using Laser Writer patterning followed by metal deposition (E-beam evaporation) and lift-off process. In the fourth step, 20 nm thick HfO<sub>2</sub> was grown by ALD in a Cambridge NanoTech reactor at 150 °C to serve as the high- $\kappa$  top-gate dielectric, where tetrakis(dimethylamido)hafnium  $[Hf(NMe_2)_4]$  and  $H_2O$  were used as the precursors and nitrogen  $(N_2)$  as the carrier gas.<sup>[54]</sup> The sequence of pulses for one deposition cycle of  $HfO_2$  is  $H_2O$  (0.015 s)/N<sub>2</sub> (20 s)/ Hf(NMe<sub>2</sub>)<sub>4</sub> (0.15 s)/N<sub>2</sub> (30 s). Prior to top gate metal formation, Ar<sub>2</sub>based plasma was used to define the via-holes that connect the source/ drain metal and top-gate metal layers where necessary. Finally, after electrodes patterning by Laser Writer, 5/70 nm Ti/Au top metal layer was formed by E-beam evaporation and subsequent lift-off process in acetone. During the fabrication, poly(methyl methacrylate) was used as photoresist for EBL and AZ1512 photoresist was used for Laser Writer patterning.

*Electrical Characterization*: All electrical measurements were carried out in air at room temperature. The current–voltage characteristics of the transistor and voltage transfer characteristics of logic gates were measured using a Cascade probe station with a HP4155B semiconductor parameter analyzer. For dynamic characterization, a digital waveform generator was used as the input source and the output signal was detected by a digital oscilloscope.

# **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

## Acknowledgements

L.W. and L.C. contributed equally to this work. K.-W.A. supervised this project. K.-W.A. is grateful for the support by A\*STAR Science and Engineering Research Council Grant (No. 152-70-00013), National Research Foundation Competitive Research Programs (NRF-CRP15-2015-01 and NRF-CRP15-2015-02), and by the National Research Foundation, Prime Minister's Office, Singapore under its medium sized center program.

# **Conflict of Interest**

The authors declare no conflict of interest.

## **Keywords**

chemical vapor deposition (CVD), integrated circuits, memory,  $\mathsf{MoS}_{\mathsf{2}},$  transistors

Received: April 17, 2019

- Revised: May 7, 2019

- Published online: June 3, 2019

- K. S. Novoselov, A. K. Geim, S. Morozov, D. Jiang, M. Katsnelson, I. Grigorieva, S. Dubonos, A. A. Firsov, *Nature* 2005, 438, 197.

- [2] A. C. Neto, F. Guinea, N. M. Peres, K. S. Novoselov, A. K. Geim, *Rev. Mod. Phys.* **2009**, *81*, 109.

- [3] S. Manzeli, D. Ovchinnikov, D. Pasquier, O. V. Yazyev, A. Kis, Nat. Rev. Mater. 2017, 2, 17033.

- [4] L. Liao, Y.-C. Lin, M. Bao, R. Cheng, J. Bai, Y. Liu, Y. Qu, K. L. Wang, Y. Huang, X. Duan, *Nature* **2010**, 467, 305.

- [5] Y. Wu, Y.-m. Lin, A. A. Bol, K. A. Jenkins, F. Xia, D. B. Farmer, Y. Zhu, P. Avouris, *Nature* **2011**, *472*, 74.

- [6] D. Jariwala, V. K. Sangwan, L. J. Lauhon, T. J. Marks, M. C. Hersam, ACS Nano 2014, 8, 1102.

- [7] B. Tang, Z. G. Yu, L. Huang, J. Chai, S. L. Wong, J. Deng, W. Yang, H. Gong, S. Wang, K. W. Ang, Y. W. Zhang, D. Chi, ACS Nano 2018, 12, 2506.

- [8] K. Kaasbjerg, K. S. Thygesen, K. W. Jacobsen, Phys. Rev. B 2012, 85, 115317.

- [9] B. Radisavljevic, A. Radenovic, J. Brivio, i. V. Giacometti, A. Kis, Nat. Nanotechnol. 2011, 6, 147.

- [10] T. Roy, M. Tosun, J. S. Kang, A. B. Sachid, S. B. Desai, M. Hettick, C. C. Hu, A. Javey, ACS Nano 2014, 8, 6259.

- [11] M. S. Fuhrer, J. Hone, Nat. Nanotechnol. 2013, 8, 146.

- [12] J. Wang, Q. Yao, C. W. Huang, X. Zou, L. Liao, S. Chen, Z. Fan, K. Zhang, W. Wu, X. Xiao, Adv. Mater. 2016, 28, 8302.

- [13] S. Kim, A. Konar, W. S. Hwang, J. H. Lee, J. Lee, J. Yang, C. Jung, H. Kim, J. B. Yoo, J. Y. Choi, Y. W. Jin, S. Y. Lee, D. Jena, W. Choi, K. Kim, *Nat. Commun.* **2012**, *3*, 1011.

- [14] H. Wang, L. Yu, Y.-H. Lee, Y. Shi, A. Hsu, M. L. Chin, L.-J. Li, M. Dubey, J. Kong, T. Palacios, *Nano Lett.* **2012**, *12*, 4674.

- [15] B. Radisavljevic, M. B. Whitwick, A. Kis, ACS Nano 2011, 5, 9934.

- [16] X. Ling, Y. Lin, Q. Ma, Z. Wang, Y. Song, L. Yu, S. Huang, W. Fang, X. Zhang, A. L. Hsu, Y. Bie, Y. H. Lee, Y. Zhu, L. Wu, J. Li, P. Jarillo-Herrero, M. Dresselhaus, T. Palacios, J. Kong, *Adv. Mater.* **2016**, *28*, 2322.

- [17] M. Zhao, Y. Ye, Y. Han, Y. Xia, H. Zhu, S. Wang, Y. Wang, D. A. Muller, X. Zhang, Nat. Nanotechnol. 2016, 11, 954.

- [18] R. Cheng, S. Jiang, Y. Chen, Y. Liu, N. Weiss, H. C. Cheng, H. Wu, Y. Huang, X. Duan, *Nat. Commun.* **2014**, *5*, 5143.

- [19] D. Kufer, G. Konstantatos, Nano Lett. 2015, 15, 7307.

- [20] X. Duan, C. Wang, A. Pan, R. Yu, X. Duan, Chem. Soc. Rev. 2015, 44, 8859.

- [21] Y. Shi, H. Li, L. J. Li, Chem. Soc. Rev. 2015, 44, 2744.

- [22] J. N. Coleman, M. Lotya, A. O'Neill, S. D. Bergin, P. J. King, U. Khan, K. Young, A. Gaucher, S. De, R. J. Smith, I. V. Shvets, S. K. Arora, G. Stanton, H.-Y. Kim, K. Lee, G. T. Kim, G. S. Duesberg, T. Hallam, J. J. Boland, J. J. Wang, J. F. Donegan, J. C. Grunlan, G. Moriarty, A. Shmeliov, R. J. Nicholls, J. M. Perkins, E. M. Grieveson, K. Theuwissen, D. W. McComb, P. D. Nellist, V. Nicolosi, *Science* 2011, 331, 568.

- [23] L. K. Tan, B. Liu, J. H. Teng, S. Guo, H. Y. Low, H. R. Tan, C. Y. Chong, R. B. Yang, K. P. Loh, *Nanoscale* **2014**, *6*, 10584.

- [24] W. Jeon, Y. Cho, S. Jo, J. H. Ahn, S. J. Jeong, Adv. Mater. 2017, 29, 1703031.

- [25] K. Kang, S. Xie, L. Huang, Y. Han, P. Y. Huang, K. F. Mak, C.-J. Kim, D. Muller, J. Park, *Nature* **2015**, *520*, 656.

- [26] S. Najmaei, Z. Liu, W. Zhou, X. Zou, G. Shi, S. Lei, B. I. Yakobson, J.-C. Idrobo, P. M. Ajayan, J. Lou, *Nat. Mater.* **2013**, *12*, 754.

- [27] Y. C. Lin, W. Zhang, J. K. Huang, K. K. Liu, Y. H. Lee, C. T. Liang, C. W. Chu, L. J. Li, *Nanoscale* **2012**, *4*, 6637.

- [28] Y. Zhan, Z. Liu, S. Najmaei, P. M. Ajayan, J. Lou, Small 2012, 8, 966.

- [29] S. Vangelista, E. Cinquanta, C. Martella, M. Alia, M. Longo, A. Lamperti, R. Mantovan, F. B. Basset, F. Pezzoli, A. Molle, *Nanotechnology* **2016**, *27*, 175703.

- [30] X. Ling, Y.-H. Lee, Y. Lin, W. Fang, L. Yu, M. S. Dresselhaus, J. Kong, *Nano Lett.* **2014**, *14*, 464.

- [31] S. Wachter, D. K. Polyushkin, O. Bethge, T. Mueller, *Nat. Commun.* **2017**, *8*, 14948.

- [32] L. Yu, Y.-H. Lee, X. Ling, E. J. Santos, Y. C. Shin, Y. Lin, M. Dubey, E. Kaxiras, J. Kong, H. Wang, *Nano Lett.* **2014**, *14*, 3055.

## **ADVANCED** SCIENCE NEWS

www.advancedsciencenews.com

- [33] T. Das, X. Chen, H. Jang, I. K. Oh, H. Kim, J. H. Ahn, Small 2016, 12, 5720.

- [34] D. Dumcenco, D. Ovchinnikov, K. Marinov, P. Lazic, M. Gibertini, N. Marzari, O. L. Sanchez, Y.-C. Kung, D. Krasnozhon, M.-W. Chen, ACS Nano 2015, 9, 4611.

- [35] S. Wu, C. Huang, G. Aivazian, J. S. Ross, D. H. Cobden, X. Xu, ACS Nano 2013, 7, 2768.

- [36] Y. Woo, W. Hong, S. Y. Yang, H. J. Kim, J. H. Cha, J. E. Lee, K. J. Lee, T. Kang, S. Y. Choi, *Adv. Electron. Mater.* **2018**, *4*, 1800251.

- [37] H. Yu, M. Liao, W. Zhao, G. Liu, X. J. Zhou, Z. Wei, X. Xu, K. Liu, Z. Hu, K. Deng, S. Zhou, J. A. Shi, L. Gu, C. Shen, T. Zhang, L. Du, L. Xie, J. Zhu, W. Chen, R. Yang, D. Shi, G. Zhang, ACS Nano 2017, 11, 12001.

- [38] W. H. Chae, J. D. Cain, E. D. Hanson, A. A. Murthy, V. P. Dravid, *Appl. Phys. Lett.* 2017, 111, 143106.

- [39] K. Kang, K. H. Lee, Y. Han, H. Gao, S. Xie, D. A. Muller, J. Park, *Nature* 2017, 550, 229.

- [40] D. B. Strukov, G. S. Snider, D. R. Stewart, R. S. Williams, *Nature* 2008, 453, 80.

- [41] J. J. Yang, D. B. Strukov, D. R. Stewart, Nat. Nanotechnol. 2013, 8, 13.

- [42] R. Ge, X. Wu, M. Kim, J. Shi, S. Sonde, L. Tao, Y. Zhang, J. C. Lee, D. Akinwande, *Nano Lett.* **2018**, *18*, 434.

- [43] Y. Shi, X. Liang, B. Yuan, V. Chen, H. Li, F. Hui, Z. Yu, F. Yuan, E. Pop, H. S. P. Wong, M. Lanza, *Nat. Electron.* 2018, 1, 458.

- [44] M. Wang, S. Cai, C. Pan, C. Wang, X. Lian, Y. Zhuo, K. Xu, T. Cao, X. Pan, B. Wang, S.-J. Liang, J. J. Yang, P. Wang, F. Miao, *Nat. Electron.* **2018**, *1*, 130.

- [45] V. K. Sangwan, H.-S. Lee, H. Bergeron, I. Balla, M. E. Beck, K.-S. Chen, M. C. Hersam, *Nature* 2018, 554, 500.

- [46] L. Wang, W. Liao, S. L. Wong, Z. G. Yu, S. Li, Y. F. Lim, X. Feng, W. C. Tan, X. Huang, L. Chen, L. Liu, J. Chen, X. Gong, C. Zhu, X. Liu, Y. W. Zhang, D. Chi, K.-W. Ang, *Adv. Funct. Mater.* **2019**, *29*, 1901106.

- [47] L. Wang, L. Wang, K.-W. Ang, A. V.-Y. Thean, G. Liang, in 2018 IEEE International Electron Devices Meeting (IEDM), IEEE, Piscataway, NJ 2018, p. 24.5.1.

- [48] J. J. Yang, M. D. Pickett, X. Li, D. A. Ohlberg, D. R. Stewart, R. S. Williams, *Nat. Nanotechnol.* 2008, *3*, 429.

- [49] A. N. Enyashin, M. Bar-Sadan, L. Houben, G. Seifert, J. Phys. Chem. C 2013, 117, 10842.

- [50] J.-Y. Noh, H. Kim, Y.-S. Kim, Phys. Rev. B 2014, 89, 205417.

- [51] Z. G. Yu, Y. W. Zhang, B. I. Yakobson, Nano Lett. 2015, 15, 6855.

- [52] Z. Wang, S. Joshi, S. E. Savel'ev, H. Jiang, R. Midya, P. Lin, M. Hu, N. Ge, J. P. Strachan, Z. Li, Q. Wu, M. Barnell, G. L. Li, H. L. Xin, R. S. Williams, Q. Xia, J. J. Yang, *Nat. Mater.* **2017**, *16*, 101.

- [53] Y. F. Lim, K. Priyadarshi, F. Bussolotti, P. K. Gogoi, X. Cui, M. Yang, J. Pan, S. W. Tong, S. Wang, S. J. Pennycook, K. E. J. Goh, A. T. S. Wee, S. L. Wong, D. Chi, ACS Nano 2018, 12, 1339.

- [54] P. Xia, X. Feng, R. J. Ng, S. Wang, D. Chi, C. Li, Z. He, X. Liu, K.-W. Ang, *Sci. Rep.* **2017**, *7*, 40669.